|

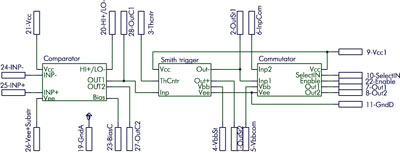

О. Дворников, В. Чеховский, А. Петрович Микросхема АФ011В для высокоточных временных измеренийНа биполярном аналоговом БМК разработана микросхема, состоящая из быстродействующего компаратора, триггера Шмидта и двухканального коммутатора. Микросхема имеет универсальную структуру и позволяет за счет различного соединения выводов и подключения двух внешних резисторов получить дискриминаторы для высокоточных временных измерений сигналов в полосе частот от 10 Гц до 200 МГц. В различной радиоэлектронной аппаратуре (РЭА) требуется с большой временной точностью определить момент поступления входного сигнала. Чаще всего для этого применяют дискриминаторы с постоянным порогом (ДПП), которые представляют собой компараторы напряжения с постоянным смещением (порогом переключения) одного из входов. При превышении входным сигналом порога выход компаратора переключается и сигнализирует о моменте поступления сигнала с амплитудой, превышающей порог. Для обеспечения высокой временной точности применяемые в ДПП компараторы должны иметь минимальную задержку переключения и слабую зависимость задержки от дифференциального входного напряжения. Ряд зарубежных фирм выпускает быстродействующие компараторы, которые можно использовать в этих целях: MAX905/906, MAX915/916, MAX9685/9687, MAX9686/9698, AD96685, AD96687. Специально для ДПП была разработана отечественная ИС 8-канального компаратора D0M Disc-8-3 [1,2]. Наложение шума на сигнал может привести к неоднократному срабатыванию компаратора при превышении сигналом порога и тем самым к появлению коротких ложных импульсов. Для устранения ложных срабатываний в компараторы вводят гистерезис, который, к сожалению, ограничивает минимальную амплитуду регистрируемых сигналов [3]. Главной задачей при разработке микросхемы АФ011В было создание универсального набора блоков, позволяющего при использовании минимального количества внешних элементов регистрировать с высокой точностью момент поступления сигнала в диапазоне частот от 10 Гц до 200 МГц. Для решения поставленной задачи на аналоговом базовом матричном кристалле АБМК_1_2 [4] была реализована ИС, блок-схема которой приведена на рис. 1. ИС состоит из быстродействующего компаратора, триггера Шмидта и двухканального коммутатора.

Для обеспечения универсальности были применены следующие решения:

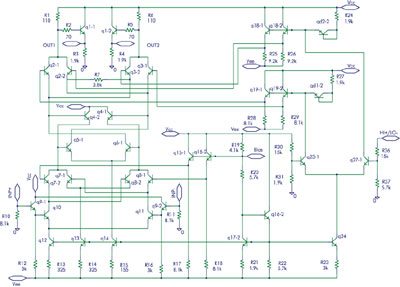

Основой ИС является компаратор, показанный на рис. 2, который построен по классической схеме быстродействующих усилителей: преобразование входного напряжения в ток дифференциальным каскадом Q10, Q11; усиление тока каскадами Джильберта; обратное преобразование ток-напряжение на низкоомных резисторах R1, R6; передача усиленного напряжения на нагрузку Out1, Out2 через эмиттерные повторители Q1-1, Q1-2. Входные эмиттерные повторители Q9-1, Q9-2 уменьшают входной ток смещения и сдвигают потенциалы на базах Q10, Q11 для обеспечения симметричного диапазона допустимого входного сигнала ±1,1 В. Изменение разности потенциалов на базах Q2-Q3 приводит к изменению усиления и даже инверсии полярности. Для управления усилением используются эмиттерные повторители на транзисторах Q18, Q19, базовый потенциал которых определяется сопротивлением R24, R27 и величиной тока, переключаемой дифференциальным каскадом Q23-1, Q27-1. Рисунок 2. Быстродействующий компаратор Триггер Шмидта и выходной коммутатор используют традиционные ЭСЛ схемотехнические решения. Основное назначение АФ011В - работа во входных каскадах электронно-сч╦тных частотомеров, поэтому для ИС нормируются параметры, привед╦нные в табл. 1. Таблица 1. Основные параметры АФ011В

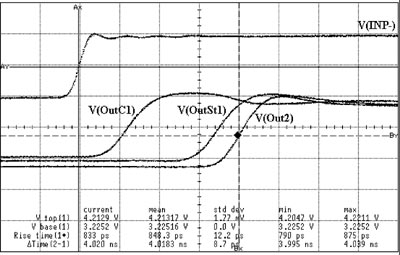

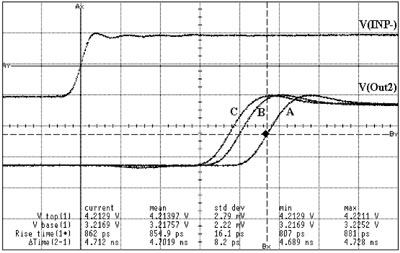

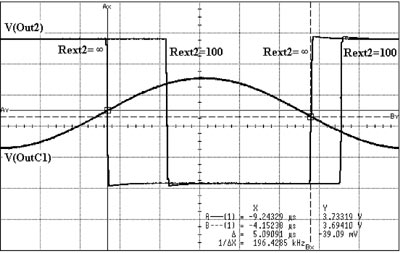

Быстродействие ИС было изучено с помощью двухканального широкополосного осциллографа 54830B "Infiniium" фирмы Hewlett-Packard. Так как только выходной каскад коммутатора может работать с 50-Ом нагрузкой при применении дополнительного источника опорного напряжения, то выходной сигнал всех основных узлов ИС регистрировался с помощью делителя 1:10 с входной ╦мкостью 10 пФ и сопротивлением 10 МОм. При этом точность определения быстродействия была ограничена временем нарастания сигнала осциллографа, которое составляет < 0,450 нс для 50-Ом входа осциллографа и < 0,550 нс при использовании делителя. Типичные результаты измерений показаны в табл. 2 и на рис. 3-5. Зависимость задержки распространения

ИС собрана в 28-выводном планарном металлокерамическом корпусе 4119.28-1Н. Следует отметить, что проектирование ИС на БМК позволяет при необходимости быстро и с минимальными затратами изменить как внутреннюю структуру, так и уровень электропараметров, например, получить двухканальный вариант. Литература

|

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

PDFs | Новости | Литература | Схемы | Форум | Блоги | Реклама |

Микросхема АФ011В для высокоточных временных измерений. Биполярный аналоговый БМК. Дискриминатор для высокоточных временных измерений сигналов. Радиоэлектронная аппаратура. Быстродействующий компаратор. ИС 8-канального компаратора D0M Disc-8-3. Превышение порога на 100 мВ. Быстродействие блоков ИС АФ011В.

Микросхема АФ011В для высокоточных временных измерений. Биполярный аналоговый БМК. Дискриминатор для высокоточных временных измерений сигналов. Радиоэлектронная аппаратура. Быстродействующий компаратор. ИС 8-канального компаратора D0M Disc-8-3. Превышение порога на 100 мВ. Быстродействие блоков ИС АФ011В.