|

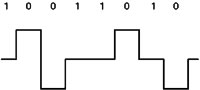

Т. Келин, Д. Супонников Аппаратная реализация двоичной полностью цифровой системы фазовой автоподстройки частотыСистемы фазовой автоподстройки частоты (ФАПЧ), выполненные в полностью цифровом варианте, то есть без применения аналоговых элементов, таких как фильтры низких частот (ФНЧ) и генератор, управляемый напряжением (ГУН), широко применяются во многих БИС для телекоммуникаций, где необходимо восстановление тактовой частоты передающей системы. Отсутствие дискретных аналоговых компонентов в такой схеме позволяет добиться высокой повторяемости параметров при одновременно меньшей стоимости узла подстройки частоты. Рассмотрен типичный пример реализации узла полностью цифровой системы фазовой автоподстройки частоты (ПЦСФАПЧ, английская нотация - DPLL) на БИС программируемой логики (ПЛИС) фирмы Altera. Описание аппаратурной части на языке Verilog позволяет без затруднений перенести узел на ПЛИС других производителей, например, Xilinx, Actel и Lattice. Введение В предыдущей статье ("Chip News", ╧ 9, 2002, с. 16) была подробно рассмотрена блок-схема ПЦСФАПЧ и сделан анализ широко применяемых петлевых последовательных фильтров, служащих целям повышения помехоустойчивости системы. Там же описан фильтр случайных блужданий с изменяющимся значением сброса, использование которого позволяет добиться хороших динамических характеристик петли, не проигрывая в помехозащищ╦нности. Ниже рассмотрим реализацию и применение такого узла в реальной системе. Постановка задачи В процессе работы с телекоммуникационным оборудованием возникла необходимость подключения оригинального модуля обработки сигналов к сигнальным линиям интерфейса ISDN-BRI в точке S, соответствующего спецификации ITU-T I.430. Физическая конфигурация этого интерфейса имеет одно сетевое окончание, два нагрузочных сопротивления (одно в сетевом окончании, другое - на конце шины) и предусматривает возможность подключения к шине нескольких оконечных устройств [1]. Электрическая спецификация интерфейса ITU-T G.961 предусматривает передачу битов данных троичным кодом (рис. 1) с чередованием полярности импульсов - биполярный код AMI. Данный код обладает недостатком, связанным с тем, что если переда╦тся длинная последовательность единиц, выделение тактовой частоты может быть ухудшено. В отдельных вариантах исполнения аппаратуры, использующей такой код, данные специально скремблируются, чтобы облегчить синхронизацию при╦мника, но для интерфейса I.430 скремблирование не предусмотрено. Рассматривая практически применяемые системы связи, построенные на этом интерфейсе, можно убедиться в том, что, в зависимости от состояния канала, длительность "периода молчания" достигает длины одного кадра. При этом требования спецификации устанавливают недопустимость рассинхронизации консольной и задающей аппаратуры даже в случае "молчания" в линии до 40 кадров, то есть 10 мс. Таким образом, требовалось построить узел, обеспечивающий над╦жную синхронизацию при╦мопередатчика оконечного устройства с задающей аппаратурой. Рисунок 1. Форма сигнала базового пользовательского интерфейса

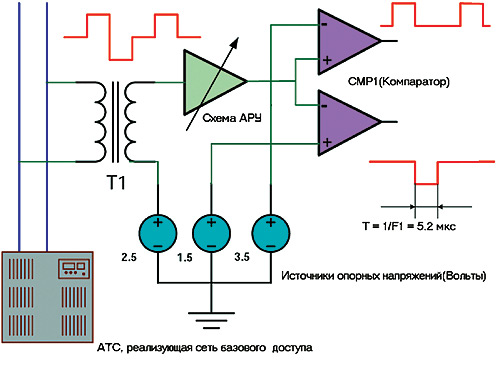

Использование ПЦСФАПЧ для построения узла синхронизатора Для обеспечения битовой синхронизации, то есть получения на выходе узла последовательности импульсов, каждый перепад которых, положительный или отрицательный, приходится на середину битового интервала входного сигнала, целесообразно использовать ПЦСФАПЧ, имеющую достаточную инертность, позволяющую предотвратить "уход" фазы на выходе узла синхронизатора за время передачи длинной серии единиц. В нашем случае, такие интервалы могут достигать 240 мкс, при отсутствии активизированного оконечного оборудования на шине. При этом длительность одного битового интервала равна 5,2 мкс, что эквивалентно скорости передачи данных с частотой 192 кГц. Возможны и другие варианты исполнения узла, как, например, использование сч╦тчика, перезагружаемого по перепаду входного сигнала, но такой синхронизатор не будет обладать каким-либо запасом помехоустойчивости и, кроме того, очень требователен к точности установки частоты задающего генератора в проектируемой системе. Особенности включения ПЦСФАПЧ в схему со смешанными сигналами Рассматриваемое устройство, содержащее узел синхронизатора, представляет собой аналогово-цифровую схему, где сигналы, поступающие на вход с шинного интерфейса, являются аналоговыми, а работа по синхронизации и выделению битов входной последовательности вед╦тся цифровыми схемами стандарта LVTTL или LVCMOS. Для сопряжения уровней сигнала используемого интерфейса c логическими уровнями цифровой части системы может быть примен╦н аналого-цифровой преобразователь, при использовании в дальнейшем тракте обработки цифрового процессора обработки сигналов (ЦПОС) или же компаратор, выделяющий положительные и отрицательные импульсы троичного кода AMI. В описываемом узле использование ЦПОС избыточно, и применена схема, представленная на рис. 2. Потенциалы "земли" оборудования, реализующего сетевое окончание и "земли" оконечной аппаратуры могут различаться, кроме этого, по сигнальным парам интерфейса часто переда╦тся постоянное напряжение для питания терминалов. В силу указанных причин, входной сигнал, во избежание нежелательного влияния синфазного напряжения, пода╦тся на изолирующий трансформатор Т1, после чего на компараторе СMP1 выделяются положительные и отрицательные импульсы уровня LVTTL, которые могут поданы непосредственно на вход узла синхронизатора. Схема АРУ необязательна, но е╦ использование актуально при нестабильных или заранее неизвестных уровнях сигнала передатчиков на шине, что может являться следствием затухания в линии невысокого качества. Рисунок 2. Схема выделения однополярных импульсов из линейнго AMI кода

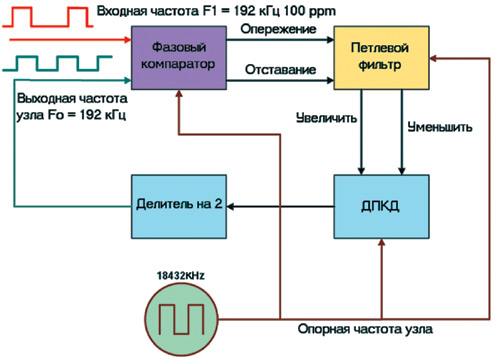

Аппаратная реализация ПЦСФАПЧ в узле синхронизатора На рис. 3 представлена блок-схема узла, в состав которого был включен синхронизатор. Установленная в модуле микросхема семейства ACEX EP1K50TC144 с успехом позволила реализовать восемь узлов синхронизации при необходимом их быстродействии. Рисунок 3. Блок-схема узла выделения частоты синхронизации

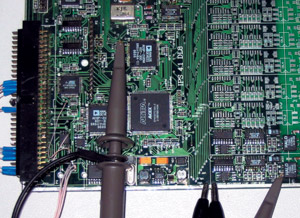

Исходная задача состояла в том, чтобы восстановить тактовую синхронизацию частотой F1 = 192 кГц. При этом частота тактового сигнала, подаваемого на БИС программируемой логики, была выбрана кратной F1 и достаточно высокой для обеспечения небольшой величины дрожания фазы. Также, в процессе анализа временных задержек в САПР "MAXPlus+II Baseline" было найдено ограничение максимальной частоты сверху. В результате оптимальная частота узла синхронизатора составила 18432 кГц, что в 96 раз превысило частоту передачи данных по шине обслуживаемого интерфейса. Базовый коэффициент делителя с переменным коэффициентом деления (ДПКД) мы выбрали в два раза меньший, то есть 48. Обусловлено это было желанием получить на выходе сигнал со скважностью 2. Для этого делитель на 2 включен непосредственно после выхода ДПКД. Это решение необязательное и, если его не реализовывать, коэффициент деления L будет равным 96, что позволит уменьшить дрожание фазы, правда, в обмен на уменьшение полосы захвата. Поэтому шаг подстройки оказался равным: TC = 2/18432 кГц = 1,09╥10-7 с. Таким образом, ширина полосы удержания узла: B0 = 2/TC(L²√1) = 2(/1,09╥10-7(48²√1)) ~ 8 кГц что составляет около 4% от базовой частоты F1 = 192 кГц и много больше нестабильности, определяемой I.430(8.1.2) [3]. Ширина полосы захвата для глубины петлевого фильтра N = 8 и частоты петли с разомкнутым контуром регулирования f0 = 192 кГц: Требованиям же параграфа 8.2.2 спецификации [3], которые устанавливают допустимые пределы дрожания фазы восстановленного сигнала синхронизации в пределах 7%, узел удовлетворяет, что наглядно было отражено в предыдущей статье. Выбор языка описания аппаратуры (в английской нотации - HDL) определялся во многом возможностью переноса полученного решения на платформы, отличные от ПЛИС фирмы Altera. Verilog HDL, как мы посчитали, наиболее подходит для этих целей в силу распростран╦нной поддержки различными САПР и прозрачности синтаксических конструкций. Иерархически описание узла включает в себя пять модулей, определ╦нных в файлах с соответствующими именами. Это модули "фильтр случайных блужданий со значением сброса 0", "фильтр случайных блужданий с переменным значением сброса", "фазовый компаратор", "делитель частоты и устройство управления фазой", "ПЦСФАПЧ - главный модуль проекта". Указанные файлы доступны для загрузки по адресу www.evm90.com/dpll/dpll.zip. Фазовый компаратор производит сравнение фазы выходного синхросигнала и последовательности данных интерфейса на каждом положительном перепаде входного потока. При этом компаратор имеет релейную характеристику [2], что да╦т выигрыш по аппаратным затратам, но, с другой стороны, повышает инертность контура регулирования, что, впрочем, в нашем случае не критично. Решение о сравнении фаз переда╦тся в петлевой фильтр, с глубиной составляющих его N-фильтра 8 и M-фильтра 32. Защ╦лкивание сигналов фазового компаратора происходит по положительному перепаду общей опорной тактовой частоты узла (MainClock). Отметим, что для над╦жной работы узла все процессы в модулях синхронны именно с этим сигналом, это позволяет избежать неопредел╦нных состояний регистров и добиться устойчивой работы синхронизатора в различных вариантах имплементации. Петлевой фильтр, в свою очередь, вырабатывает сигналы Positive и Negative, управляющие сдвигом фазы выходной частоты посредством устройства управления фазой. Последнее базируется на сч╦тчике, значение которого увеличивается на 2 в случае отставания фазы и не увеличивается вовсе в случае опережения. Данные операции полностью соответствуют "врезанию" дополнительного импульса или "вычеркиванию" в случае применения не ДПКД, а делителя с фиксированным коэффициентом деления. При отсутствии сигналов регулирования фазы значение инкремента сч╦тчика равно единице и в этом случае установившаяся частота на выходе петли будет равна f0 = 18432 кГц /2╥48 = 192 кГц Общий вид системы с ПЛИС, ресурсами которой был реализован узел ПЦСФАПЧ, показан на рис. 4. Рисунок 4. Фрагмент модуля, в состав которого включен узел синхронизации

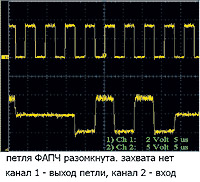

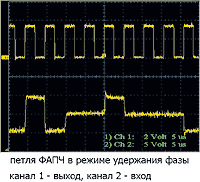

Практически полученный результат проверен на установленном оборудовании, поддерживающем базовый пользовательский интерфейс, соответствующий спецификации ITU-T I.430, и показал полную работоспособность системы. При разомкнутом контуре (например, вход последовательности данных закорочен на "массу") регулирования не происходит, и входные данные свободно "скользят" вдоль выходного синхросигнала (рис. 5). В случае же замкнутой петли узел осуществляет захват фазы входного сигнала, при этом каждый спадающий фронт выходной частоты приходится на середину битового интервала данных, передаваемых по шине (рис. 6). Далее эта частота может быть использована для фиксации поступающих битов и их последующей обработке.

Литература

|

Аппаратная реализация двоичной полностью цифровой системы фазовой автоподстройки частоты.

Аппаратная реализация двоичной полностью цифровой системы фазовой автоподстройки частоты.