|

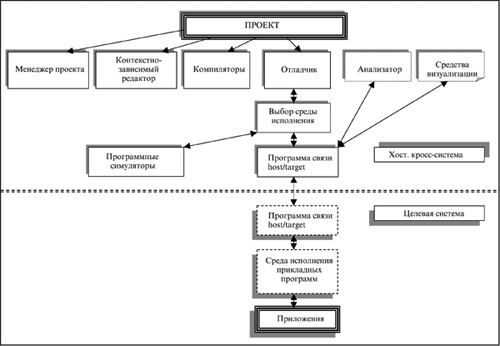

В. Никольский, В. Володин, Ю. Александров, А. Крымов, Г. Орлов, А. Глушков, А. Полтавцев, Я. Петричкович, Т. Солохина Интегрированная среда разработки и отладки программ для модулей сигнальных контроллеров на базе ИМС платформы МУЛЬТИКОРВ предыдущем номере журнала был описан опыт создания первой отечественной ИМС на базе новой открытой платформы "МУЛЬТИКОР" - сигнального контроллера мини-конфигурации МУЛЬТИКОР-11 (МС-11). МС-11 относится к новому классу приборов - Цифровых Сигнальных Контроллеров или DSC (Digital Signal Controller) и объединяет в одном чипе, разрабатываемом как система на кристалле (SoC - System-on-the Chip), достоинства RISC-контроллера и встроенного процессора обработки сигналов. DSC образно сравнивались с мифическими суперсуществами - Кентаврами, которые имеют мыслящую человеческую голову (RISC-ядро) и быстрые ноги (DSP-ядро).Тем не менее, иметь разумную голову - это ещ╦ не гарантия того, что Кентавр побежит в нужном направлении в актуальном технологическом забеге, в котором участвуют лидирующие электронные компании мира. Для этого ему нужно, как минимум, вложить в голову маршрут, то есть соответствующую программу. Заметим, что все зрители этого забега уже делают свои ставки: добежит Кентавр до цели или не добежит? Полагаем, что добежит. По крайней мере, вс╦ его снаряжение (то есть средства проектирования и отладки программного обеспечения) скроено удобно, добротно и по стандартным меркам. К сожалению, в рамках журнальной статьи трудно проанализировать все аспекты разработанной комплексной системы проектирования программного обеспечения (ПО). Поэтому состав средств проектирования рассмотрен очень кратко. Для наглядности привед╦н пример практического применения этих средств - создание прикладной программы MP3-декодирования, которая будет реализована в качестве одного из мультимедийных режимов работы перспективного отечественного коммуникационного процессора МУЛЬТИКОМ (MCom-xx) для систем связи третьего поколения. Помимо системы проектирования чипов, платформа МУЛЬТИКОР разрабатывается так же, как комплексная система проектирования программного обеспечения для них. Она обеспечивает поддержку программных проектов на всех стадиях разработки для нескольких серий чипов на базе платформы МУЛЬТИКОР, включая серии для ИМС МС-11xx/МС-12xx/MC-01xx/MC-02xx/MCom-xx/MGraph-xx и так далее. Программное обеспечение платформы МУЛЬТИКОР включает ассемблеры обоих процессорных ядер (RISC и DSP), компилятор языка C, программный симулятор кристаллов серий MC-ХХ (симуляторы ядер и устройств ввода/вывода), символьные и двоичные отладчики, объедин╦нные в интегрированную среду MCS (MultiCore Studio), а также аппаратно-программный отладчик на базе XILINX FPGA прототипа ИМС МС-xxxx. Эффективное программирование систем на базе ИМС DSC-платформы МУЛЬТИКОР основано, прежде всего, на использовании чипами в качестве одного из двух процессорных ядер архитектурного аналога стандартного RISC-ядра MIPS32╝-архитектуры собственной разработки ЭЛВИС. Эффективное программирование систем на базе ИМС DSC платформы МУЛЬТИКОР основано, прежде всего, на использовании чипами в качестве одного из двух процессорных ядер RISC-ядра, совместимого по прикладному программному обеспечению с процессорами MIPS-архитектуры. Отметим также, что DSC серий МУЛЬТИКОР максимально используют столько стандартных решений, сколько это возможно: стандарты представления данных, стандартное RISC-ядро, стандартные периферийные и внутренние интерфейсы и так далее. RISC-ядро имеет короткий конвейер, а DSP-ядро большинство команд выполняет за такт, обеспечивая RISC-ориентированный стиль архитектуры. Кроме того, DSP-ядро обеспечивает и ряд других архитектурных решений (аппаратно поддержанные циклы, стеки, эффективное выполнение команд условий в SIMD-режимах и так далее), которые предо-ставляют пользователю широкие возможности по прикладному программированию. Следует упомянуть также гибкие возможности программного управления трафиком потоков в ИМС, внешними флагами и энергосберегающими режимами - всего не перечислишь. Поэтому рассмотрим подробнее состав предлагаемых пользователю средств программирования и отладки платформы МУЛЬТИКОР. Интегрированная среда разработки и отладки программ для модулей обработки информации на базе ИМС серии Мультикор Как отмечалось выше, для разработки и отладки программ для устройств, построенных на базе кристаллов платформы МУЛЬТИКОР, используется MultiCore Studio (MCS). MCS представляет собой интегрированную среду (IDE), обеспечивающую разработчику программ доступ ко всем инструментам (симуляторам, моделям, аппаратно-программным FPGA прототипам ИМС) из одного интерфейса и позволяющую выполнять полный цикл разработки и отладки программ. MCS включает в себя среду разработки, предназначенную для разработки, компиляции и компоновки программ для целевых устройств, построенных на базе кристаллов серий МУЛЬТИКОР. Среда разработки обеспечивает создание проекта программы, ввод и редактирование текстов модулей программы, компиляцию модулей и компоновку программы, диагностику и визуальную локализацию синтаксических ошибок, подготовку образа памяти для загрузки в целевое устройство. Среда отладки обеспечивает загрузку программ в модель памяти симулятора чипа; задание точек останова программы по адресу в программе или на строке программы; запуск программы; исполнение программы до точки останова или по шагам, с заходом в вызываемую функцию или с пропуском вызываемых функций; получение сообщений об остановах и завершении программ; чтение данных из памяти симулятора по адресу или символическому имени переменной при остановах программы; чтение и запись данных с регистров симулятора чипа (MultiCore) и запись данных в память и регистры; формирование протокола действий оператора и прочитываемых данных, использование командного файла для автоматического выполнения операторских действий интерпретатором командного файла. MCS является кросс-системой и функционирует на инструментальной машине IBM PC в среде Windows 9x или LINUX. Для размещения MCS необходимо около 30 Мбайт памяти на ж╦стком диске. Инсталляция MCS осуществляется запуском setup.exe. Структура интегрированной среды отладки и разработки приведена на рис. 1. Рисунок 1. Структура интегрированной среды отладки и разработки программ ИМС серии МУЛЬТИКОР

Графический интерфейс MCS образуют главное окно, меню системы, инструментальные кнопки, строка состояния, окно проекта и окно сообщений. Меню системы включает пункты File, Edit, View, Project, Debug, Options, Window, Help:

Инструментальные кнопки дублируют наиболее часто выполняемые операции меню работы с файлами, редактором, операции компиляции и управления отладчиком:

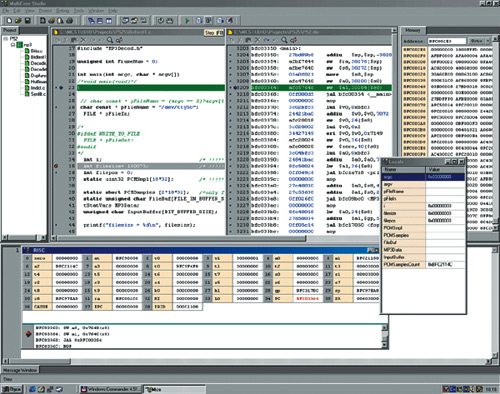

На рис. 2 привед╦н пример интерфейса MCS с открытыми окнами проекта, редактора, дизассемблера RISC-программы с курсором на исполняемой строке программы, окно сообщений, окно локальных переменных, окно памяти и регистров RISC-ядра и окна исполняемых на RISC-ядре команд, при запуске режима отладки на симуляторе ИМС МС-xxxx. Рисунок 2. Пример интерфейса MCS с открытыми окнами проекта

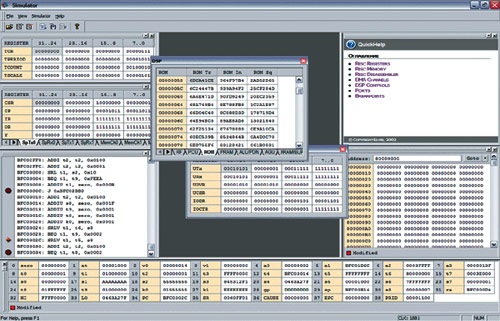

Инструменты RISC-core Инструменты для RISC-core построены на базе Free GNU toolkit и представляют собой кросс-систему для разработки программ. В состав инструментов для RISC-core входят компилятор с языка С (mgcc), ассемблер, линковщик, препроцессор, библиотекарь, утилиты для работы с кодом. Инструменты DSP-core В состав инструментов DSP-core входят ассемблер с препроцессором (elas), линковщик, библиотекарь, преобразователь форматов объектных и выполняемых файлов и утилиты. Все инструменты DSP-core построены на базе пакета binutils GNU. Ассемблер (elas) предназначен для обработки исходных текстов на языке Ассемблера и создания объектных и загружаемых файлов, которые могут выполняться на DSP-ядре. Язык Ассемблера содержит мнемонические коды для всех машинных команд масштабируемого по SIMD-типу (Single Instructions Multiple Data) DSP-ядра (ELCORE-xx). Кроме того, язык содержит мнемонические директивы, задающие дополнительные действия, которые должны быть выполнены ассемблером. В частности, они позволяют определять макрокоманды, которые позволяют кратко записывать группу команд с выполнением текстовой подстановки того или иного рода. Ассемблер последовательно обрабатывает все строки файла. При этом сначала выполняются все директивы макроподстановки, а затем полученный результат ассемблируется. После обработки всего файла выполняется окончательная обработка выражений, и те из них, которые не могут быть вычислены на этом этапе, остаются для компоновщика. Память процессора ELCORE-xx содержит 3 компоненты: область программ, область данных и область констант. Ассемблер позволяет создать код только для первых двух областей памяти и использовать имена для ссылок на область констант. Так как область констант видима только через регистр AT, в который и надо загружать соответствующие ссылки, и не доступна иным способом, то достаточно введение им╦н для констант либо прямо через set, либо через struct. При создании кода для области данных учитывается возможность использования процессора в режимах SIMD/SCALAR и, соответственно, генерирования данных вместе или без разбиения на DSP-секции. Ассемблер позволяет учесть некоторые особенности DSP-ядра и упростить программирование. В частности, он позволяет вводить простым способом в качестве аргументов все виды данных, которые имеются у DSP-процессора. Для того, чтобы DSP-ядро могло эффективно выполнять свои функции, ассемблер выполняет ряд специальных действий, например, для оптимального размещения данных. Для проверки и гарантии корректности выделения места в режиме SIMD можно использовать директивы SIMD/SCALAR. Программы состоят из последовательности исходных операторов. Маленькие и большие буквы считаются эквивалентными при записи мнемоник команд, директив, кодов условий и им╦н регистров, но отличаются во всех остальных случаях, то есть при записи меток, символьных им╦н и литерных строк. Проект программы для ИМС МС-11/01/02/xx состоит из модулей, написанных на ассемблере elas, языке С и на ассемблере для RISC-core. Модули могут компилироваться по отдельности, сборка проекта и получение образа памяти для исполнения выполняются по команде build. В MCS предусматривается отладка программ на симуляторах или с помощью программно-аппаратных отладчиков. Вызов среды отладки выполняется пут╦м выбора альтернативы в меню DEBUG. При отладке программ на программных симуляторах могут быть открыты окна симуляторов ядер СБИС платформы МУЛЬТИКОР - RISC-core, DSP-core, памяти, портов и DMA, отображающие состояния регистров устройств и протокол исполненных команд. Пример интерфейса симулятора МС-11xx привед╦н на рис. 3. Рисунок 3. Пример интерфейса симулятора МС-11xx

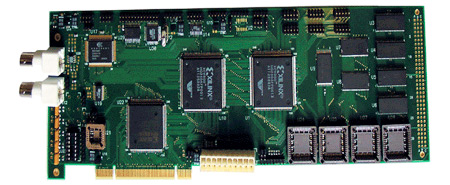

Программно-аппаратные отладчики для модулей обработки сигналов на базе ИМС платформы МУЛЬТИКОР Программно-аппаратные отладчики для модулей обработки сигналов на базе ИМС платформы МУЛЬТИКОР базируются на использовании специально разработанного в ГУП НПЦ "Элвис" модуля для эмуляции (прототайпинга) - MC-PCI-EVM. XILINX-прототипы (эмуляторы) для ИМС МС-xxxx различных серий платформы МУЛЬТИКОР формируются пут╦м реконфигурации нескольких XILINX FPGA типа Virtex, то есть посредством загрузки в них соответствующих файлов конфигураций, то есть ".bit"-файлов разработки ГУП НПЦ "Элвис". Указанный модуль входит в состав стартового набора для работы с ИМС платформы МУЛЬТИКОР - SDK-01xx. Кроме модуля MC-PCI-EVM, в состав SDK-01xx входит CD c системой инструментального ПО (MCS), соответствующей программной документацией и обучающими примерами программирования для ИМС платформы "МУЛЬТИКОР". Связь с эмулятором МС-xxxx выполняется через адаптер со стороны ПК (персонального компьютера), то есть через параллельный порт в режиме ЕРР, а со стороны МС-xxxx - через стандартный JTAG (IEEE 1149.1) интерфейс. MC-PCI-EVM (PCI-модуль аппаратного эмулятора и отладчика) предназначен для функционального моделирования и отладки конфигураций FPGA-прототипов ИМС платформы МУЛЬТИКОР (МС-11/12/01/02/xx), а также для отладки их инструментального и прикладного программного обеспечения. В дальнейшем описании модуль будет называться CENTAURUS 2K2. В качестве интерфейсов CENTAU-RUS 2K2 поддерживает:

Такое разнообразие возможных конфигураций подключения модуля да╦т возможность пользователю решать проблемы прототайпинга систем на базе ИМС МУЛЬТИКОР практически без ограничения ресурсов ввода/вывода. Работа модуля поддерживается с помощью пакета инструментального ПО, выполняемого на ПЭВМ и включающего, в том числе, инструментальное ПО платформы МУЛЬТИКОР - MCS. Архитектура CENTAURUS 2K2 (рис. 4) содержит три FPGA. Процессорные ядра располагаются в двух FPGA VIRTEX-E (максимально 2 кристалла по 1 млн. вентилей), а контроллер PCI - в FPGA SPARTAN-II (до 200 тыс. вентилей). Рисунок 4. Внешний вид модуля CENTAURUS 2K2 (MC-PCI-EVM)

Данная плата также содержит три типа памяти:

Подача питающего напряжения на CENTAURUS 2K2 осуществляется с использованием:

Для работы с эмулятором предоставляются два отладчика (mdb и gdb), обеспечивающие взаимо-действие со встроенными средствами отладки MC-xxxx через диагностический JTAG (IEEE 1149.1) интерфейс. Плата эмулятора взаимодействует с PC через JTAG-адаптер, подключаемый к параллельному порту компьютера. Отладчик MDB (MultiCoreDebugger) Mdb является низкоуровневым отладчиком и позволяет производить как диагностику DSC/процессорной платы на его основе, так и отладку его программного обеспечения. Отладчик mdb очень удобен при отладке участков кода, для которых необходим максимальный контроль за состоянием системы, примерами такого кода могут быть обработчики прерываний/исключений, подсистема виртуальной памяти OS. Отладчик mdb предоставляет пользователю доступ ко всем встроенным средствам отладки ИМС серий МУЛЬТИКОР, в частности:

В интерактивном режиме работы для удобства пользователя реализованы такие возможности, как tab-completion, command history, line-editing и другие. Отладчик позволяет выполнять команды из файлов, при этом файлы команд могут содержать комментарии и "вызовы" команд из других файлов. Отладчик также способен выполнять команды из стандартного потока ввода или одну команду из командной строки. Эти возможности отладчика позволяют использовать его как универсальный инструмент из других программ и надстроек. Такими программами могут являться интегрированная среда разработки или графический интерфейс отладчика. Кроме того, отладчик может вызываться из языка-интерпретатора (к примеру, perl) и выполнять команды под его управлением, обеспечивая скрытое для пользователя взаимодействие с нижним уровнем. Использование отладчика из других программ позволяет реализовывать циклы, условное исполнения команд и автоматически анализировать полученные результаты. Такое применение очень удобно, к примеру, для реализации наборов тестов. Отладчик GDB (GNU Debugger) Отладчик GNU GDB поддерживает стандартные возможности символьных отладчиков, в частности:

Операционная система LINUX для ИМС МС-xx В настоящее время ОС Linux является одной из самых популярных платформ программного обеспечения. На первом этапе в рамках работ по разработке ИМС МУЛЬТИКОМ Мультимедийного процессора для мобильных применений, разрабатываемого ГУП НПЦ "Элвис", проводятся работы по портированию ядра OS Linux 2.4 на платформу МУЛЬТИКОР. Ядро Linux будет содержать драйверы всех устройств, входящих в состав ИМС. Для улучшения времени отклика системы планируется внедрение Real Time расширений в ядро Linux. Далее развитие порта OS Linux должно обеспечивать построение приложений мультимедийного процессора для обработки информации, полученной по беспроводной связи в мобильных приборах и е╦ обработки. Будет создан Linux дистрибутив, включающий стандартные и широко используемые приложения и библиотеки. Кроме того, планируется создание мультимедийных библиотек, оптимизированных для платформы МУЛЬТИКОР. Таким образом, разработчики получат платформу, поддерживающую огромный набор различных устройств, коммуникационных протоколов, файловых систем, средств разработки и готовых приложений. Библиотека прикладных программ для ИМС платформы МУЛЬТИКОР С целью ускорения процесса программирования среда программирования MCS снабжается набором прикладных библиотек. Библиотеки содержат процедуры, эффективно реализованные на ассемблерах МС-ХХ. Процедуры вызываются как функции (или подпрограммы). Таблица 1. Состав библиотеки прикладных функции общего назначения

Библиотека состоит из двух частей: одна содержит универсальные средства для выполнения вычислений/обработки сигналов (табл. 1), другая набор специализированных процедур, используемых при обработке сигналов (в частности, в мультимедийных применениях для мобильных систем) (табл. 2). Таблица 2. Состав библиотеки специализированных приложений

Помимо перечисленных, в состав прикладной библиотеки предполагается включить следующие дополнительные процедуры, совместимые с Linux:

Создаваемая технология программирования должна обеспечить возможность разработки эффективного прикладного программного обеспечения для перспективных применений, включая разработку WEB-браузеров для систем мобильного Интернета на СФ-блоке мультимедийного процессора. Пример разработки прикладной программы: аудиодекодер МР3 на платформе МУЛЬТИКОР (SISD-конфигурация DSP-ядра) Программа аудиодекодера МР3 предназначена для декодирования битового потока данных, удовлетворяющего спецификациям MPEG1. Она отвечает всем требованиям стандарта ISO/IEC 11172-3 (MPEG1 audio, Layer 3), который определяет синтаксис битового потока данных и специфицирует его параметры для аудиосигналов с частотами выборки 32, 44,1 и 48 кГц. Кроме того, учтены спецификации: LSF (low sampling frequency, взята из стандарта MPEG2) и MPEG2.5 (не стандартизована ISO/IEC), что позволяет использовать более низкие выборочные частоты 16, 22,05 и 24 кГц, а также 8, 11,025 и 12 кГц (табл. 3). Таблица 3. Частота выборки a аудиосигнале

Процесс разработки программы аудиодекодера МР3 для платформы МУЛЬТИКОР включал несколько этапов. На первом этапе была разработана версия программы для IBM PC, которая в дальнейшем служила эталоном. Она написана на языке высокого уровня Си в интегрированной среде Microsoft Visual C++, имеет хорошо структурированный набор модулей, наиболее трудо╦мкие процедуры обработки алгоритмически оптимизированы. Е╦ быстродействие: время декодирования 10-с стереозаписи на Pentium-200 МГц при частоте дискретизации 44,1 кГц составляет около 2 с. Это позволяет рассчитывать на выполнение декодирования в реальном времени на MC-11 при тактовой частоте до 40 МГц. Таблица 4. Размер памяти программы декодера

На втором этапе было произведено портирование Си-кода декодера с платформы INTEL на RISC-платформу MC-11xx (MIPS), его адаптация к архитектуре RISC-ядра и особенностям Си-компилятора MC-11xx. В результате был получен программный проект декодера на Си для RISC-ядра с тождественными эталону результатами. Он был использован для временного профилирования на симуляторе MC-11. Необходимый для загрузки программы объ╦м памяти привед╦н в табл. 4, распределение временных затрат по процедурам (по результатам профилирования) - в табл. 5. Таблица 5. Декодер. Распределение затрат времени по основным процедурам обработки

Таблица 6. Декодер. Модуль синтезирующего фильтра на ассемблере DSP-ядра. Преобразование входного массива

Таблица 7. Декодер. Модуль синтезирующего фильтра на ассемблере DSP-ядра. Преобразование DCT-32

Таблица 8. Декодер. Модуль синтезирующего фильтра на ассемблере DSP-ядра.

Расч╦т гармоник для процедуры преобразования DCT-32

Таблица 9. Декодер. Модуль линейной интерполяции на ассемблере DSP-ядра. Завершающая фильтрация синтезирующего фильтра

Наиболее длительными оказались три процедуры: интерполяция выходных отсч╦тов, узел IMDCT (инверсное дискретное косинусное преобразование) и синтезирующий полифазный фильтр (SubBand Synthesis Filtering). Вместе они расходуют около 72% временного ресурса декодера. Они были перепрограммированы на Ассемблере DSP-ядра, что привело к значительному снижению времени декодирования. Итоговая программа, включающая Си-код RISC-ядра и ассемблерный код DSP-ядра, компилируется на инструментальных средствах 2-ядерного микроконтроллера МС-11xx и выполняется на его программном симуляторе. Правильность функционирования программы декодера проверяется пут╦м сравнения результатов декодирования с выходными данными эталонной программы декодера, работающей на IBM PC, и прослушивания выходного файла на стандартном цифровом аудиопроигрывателе. Подсч╦т числа тактов на симуляторе МС-11xx показал, что при тактовой частоте микроконтроллера MC-11 выше 33 МГц обработка выполняется на ПЭВМ в реальном времени. Для иллюстрации программирования DSP-ядра ниже приводятся тексты модулей синтезирующего фильтра и выходного интерполятора, написанные на ассемблере DSP. Модули выполняют три процедуры:

Все вычисления в DSP выполняются при повышенной точности, чтобы обеспечить высокое качество выходного звука декодера. Для этого данные представляются в 32-разрядном формате, коэффициенты - в 17-разрядном. Программная реализация перечисленных процедур была направлена на сокращение числа операций, в первую очередь - умножений, поскольку в расширенном формате 32╢32 разряда умножение выполняется за несколько тактов. Состояние разработки Программных средств платформы Мультикор Разработку первой версии инструментального программного обеспечения для СБИС на базе платформы "Мультикор", включая программные Симуляторы ИМС Мультикор-11/01/02 под Win98, Си-компилятор для RISC-ядра, ассемблерные средства программирования DSP-ядра "ЭЛКОР-1/2" и базовую прикладную библиотеку для DSP-ядра - планируется завершить к концу 2002 года. Разработка аппаратно-программного отладчика ИМС серий МУЛЬТИКОР (SDK на базе модуля для прототайпинга) будет закончено к началу 2003 года. ОС LINUX 2.4 для платформы МУЛЬТИКОР будет портирована к концу 2002 года. Таким образом разработчики аппаратных средств получают единую открытую отечественную программно-аппаратную платформу разработки СБИС и проектирования систем на их основе - МУЛЬТИКОР. Она сочетает возможность обеспечения миллиардной производительности в перспективной системе с л╦гкостью программирования, предоставляемой комплексом программных средств современного уровня, включая языки высокого уровня, ОСРВ, систему подготовки и отладки программ на базе симуляторов и аппаратных отладчиков. На базе предоставляемых средств может быть проведено макетирование перспективных систем на базе решений платформы МУЛЬТИКОР, которое обеспечит потенциальным потребителям СБИС платформы:

Дополнительная информация размещена на сайте ГУП НПЦ ЭЛВИС по адресу: http://www.sic-elvis.ru. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Интегрированная среда разработки и отладки программ для модулей сигнальных контроллеров на базе ИМС платформы МУЛЬТИКОР

Интегрированная среда разработки и отладки программ для модулей сигнальных контроллеров на базе ИМС платформы МУЛЬТИКОР