|

С. Гриневский, С. Дрозд, В. Емельянов, В. Переверзев, С. Шведов КМОП-ТАЙМЕР С ОЗУ И УПРАВЛЕНИЕМ ПО I2C-шине INA8583NВ 1999 году в НИКТП "Белмикросиcтемы" разработана микросхема INA8583N - таймер с ОЗУ 256x8 бит и управлением по I²C-шине. Данная микросхема предназначена для использования в аппаратуре, имеющей I²C-шину, в качестве часов/календаря/таймера/будильника/сч╦тчика внешних событий с включением каких-либо функций аппаратуры в определ╦нное время или по происшествии какого-либо события, а также для хранения какой-либо информации в свободных ячейках ОЗУ. Может использоваться в радиоаппаратуре и изделиях бытовой электроники. Отличительные особенности INA8583N:

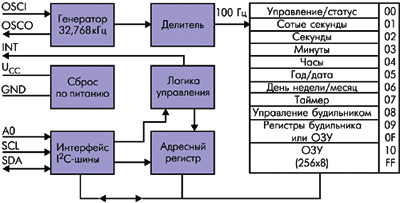

Назначение выводов микросхемы приведено в табл. 1. Структурная схема приведена на рис. 1. Таблица 1. Назначение выводов микросхемы INА8583N

Рисунок 1. Структурная схема микросхемы INA8583N

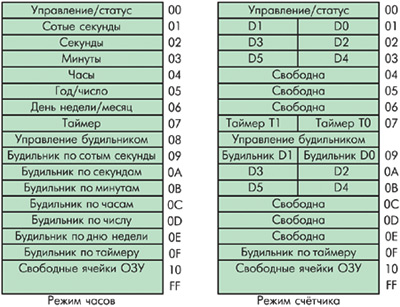

INA8583N содержит 256x8 ОЗУ с 8-бит автоинкрементируемым адресным регистром, встроенную схему генератора на 32,768 кГц, делитель частоты, интерфейс двунаправленной, двухпроводной последовательной шины (I2C) и схему сброса по питанию. Первые 8 бит ОЗУ (адреса 00÷07) разработаны как адресуемые 8-бит параллельные регистры. Первый регистр (адрес 00) используется как регистр управления/статуса. Ячейки памяти с адресами 01÷07 используются как сч╦тчики для функции часов. Ячейки памяти с адресами 08÷0F - свободные ячейки ОЗУ или могут быть запрограммированы как регистры будильника. Размещение регистров в различных режимах приведено на рис. 2. Рисунок 2. Размещение регистров в различных режимах

При загрузке регистра управления/статуса можно выбрать следующие режимы:

В режиме часов сотые секунды, секунды, минуты, часы, число, месяц (четыр╦хлетний календарь) и день недели хранятся в двоично-десятичном формате (BCD). Регистр таймера, в зависимости от выбранного режима, может считать до значения 99 дней. Режим сч╦тчика событий используется для сч╦та импульсов, поступающих на вход генератора (OSCO оста╦тся не подключенным). Сч╦тчик событий может работать до 6 цифр данных в BCD-формате. При установке бита разрешения будильника в регистре управления/статуса активизируется регистр управления будильником (адрес 08). При загрузке регистра управления будильником может быть запрограммирован один из следующих режимов:

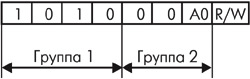

В режиме часов регистр таймера (адрес 07) может быть запрограммирован для сч╦та: сотых секунды, секунд, минут, часов или дней. Дни считаются, когда будильник не запрограммирован. Всегда, когда достигается условие будильника, устанавливается флаг будильника в регистре управления/статуса. При достижении условия будильника по таймеру будет устанавливаться флаг будильника, а при переполнении таймера установится флаг таймера. Выход прерывания (с открытым стоком) включается (активный "низкий") когда установится флаг будильника или таймера. Флаги остаются в установленном состоянии до непосредственного сброса при выполнении записи в регистр по адресу 00. Когда задана функция таймера без функций будильника, оставшиеся регистры будильника (адреса 09÷0F) могут быть использованы как свободные ячейки ОЗУ. 24- или 12-часовой формат в режиме часов может быть выбран при установке старшего значащего бита сч╦тного регистра часов (адрес 04). Год и число размещены в регистре 05. Дни недели и месяцы находятся в ячейке памяти 06. Когда читаются эти ячейки памяти, год и день недели могут быть замаскированы установкой флага маскирования в регистре управления/статуса. Это позволяет читать только значение числа и месяца. В режиме сч╦тчика событий данные записываются в BCD-формате. D5 является старшей значащей цифрой, а D0 - младшей. В этом режиме внутренний делитель отключен. Когда установлен бит разрешения будильника в регистре управления/статуса, то активизируется регистр управления будильником (адрес 08). Все функции будильника, таймера, внешнего выхода прерывания управляются содержимым регистра управления будильником. Все регистры будильника располагаются начиная с адреса 08. Будильник срабатывает, когда содержимое регистров будильника побитно совпадает с содержимым соответствующих регистров сч╦тчиков. Биты года и дня недели игнорируются при активизации режима будильника по числу. В режиме ежедневного будильника игнорируются биты месяца и числа. Когда выбран будильник по дню недели для сравнения будет выбираться бит из регистра будильника по дню недели (адрес 0Е), соответствующий дню недели, по которому активизируется будильник. Выход прерывания (с открытым стоком) программируется установкой регистра управления будильником. Он включается (активный низкий), когда устанавливается флаг будильника или флаг таймера. Кварцевый резонатор на 32,768 кГц может быть подключен к выводам OSCI (вывод1) и OSCO (вывод 2). Сигнал 100 Гц для сч╦тчиков получается с генератора через делитель в режиме часов. В режиме часов от 50 Гц или в режиме сч╦тчика событий генератор запрещается и выход генератора переключается в высокоимпедансное состояние. Это позволяет пользователю подавать частоту 50 Гц или внешний высокоскоростной сигнал событий на вход OSCI. Когда включается питание, то генерируется внутренний сигнал сброса, который очищает интерфейс I²C-шины, регистр управления/статуса и все сч╦тчики часов. После этого устройство начинает работу в режиме часов от 32,768 кГц в 24-часовом формате с 1 января 0 года с времени 0.00.00:00. На выходе прерывания будет сигнал с частотой 1 Гц (начинается с "высокого" уровня). Это можно запретить установкой бита разрешения будильника в регистре управления/статуса. Если напряжение питания падает ниже уровня сброса интерфейса I²C-шины, то вырабатывается второй внутренний сигнал сброса, который запрещает работу I²C-шины. Этот сигнал сброса не влияет на регистры сч╦тчика часов и регистр управления/статуса. Рекомендуется устанавливать флаг остановки сч╦та в регистре управления/статуса перед загрузкой истинного времени в сч╦тчики. Загрузка неверного состояния будет приводить к сбою часов, но не будет нарушать работу устройства. I²C-шина двунаправленная - двухпроводная связь между различными микросхемами или модулями. Имеется две линии, по которым осуществляется связь: линия последовательных данных (SDA) и линия последовательных тактовых импульсов (SCL). Обе линии должны соединяться с положительным полюсом источника питания через резистор, так как в микросхеме эти выходы выполняются по схеме с "открытым стоком". Передача данных может инициироваться только когда шина не занята. Один бит данных переда╦тся за один тактовый импульс. Данные на линии SDA должны быть стабильны в течение "высокого" периода тактового импульса, так как изменение на линии данных в это время будет интерпретироваться как управляющий сигнал. Перед любой передачей по I²C-шине вначале переда╦тся адрес вызываемого устройства. Адресация всегда выда╦тся с первым передаваемым байтом после процедуры старта. Формат адреса микросхемы представлен на рис. 3. Рисунок 3. Адрес INA8583N

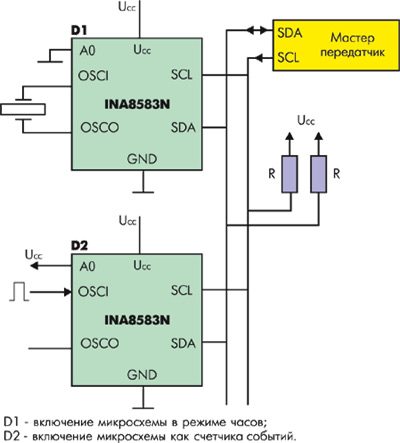

Схема включения микросхемы приведена на рис. 4. Рисунок 4. Схема применения

По всем вопросам, связанным с использованием описанной микросхемы, обращаться по тел.: (017) 277-9552, 278-3198. Факс (017) 278-2822. E-mail: belms@belms.belpak.minsk.by. |

КМОП-ТАЙМЕР С ОЗУ И УПРАВЛЕНИЕМ ПО I2C-шине INA8583N

КМОП-ТАЙМЕР С ОЗУ И УПРАВЛЕНИЕМ ПО I2C-шине INA8583N