|

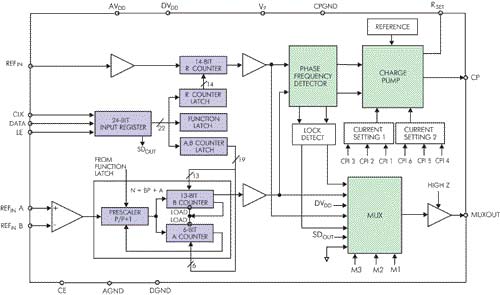

О. Стариков ФАПЧ-синтезаторы частоты типа Integer-N. Часть 3.В предыдущих статьях рассмотрены структурные схемы, принципы функционирования и базовые блоки ФАПЧ синтезаторов частот, в которых коэффициенты деления делителей задаются целым числом. Теперь рассмотрим компонентную реализацию синтезатора частоты типа Integer-N. На рис. 1 приведена функциональная схема микросхемы ADF4110 компании ANALOG DEVICES, которая представляет собой схему простого (однопетлевого) синтезатора частоты, а в табл. 1 - основные параметры ИС. Рисунок 1. Функциональная схема ФАПЧ-синтезатора частоты ADF4110

Таблица 1. Краткие технические характеристики ИМС ADF4110/ADF4111/ADF4112/ADF4113

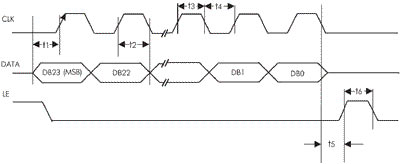

Микросхема рассчитана на максимальную входную частоту 550 МГц, работает от источника питания в диапазоне от 2,7 до 5,5 В и при необходимости может быть переведена в режим пониженного энергопотребления (программно или аппаратно). Имеет в сво╦м составе программируемый опорный делитель, двухмодульный прескалер с коэффициентами 8/9, 16/17, 32/33, 64/65, а также содержит функции программирования источника тока и антилюфтового широкого импульса (antibacklash pulse width), назначение которого было описано в предыдущей статье. Программирование производится по тр╦хпроводному последовательному интерфейсу. На вход REFIN пода╦тся сигнал частоты от внешнего образцового опорного генератора, который через входной буфер поступает на вход 14-разрядного опорного делителя 14-BIT R COUNTER с коэффициентом деления от 1 до 16383. Биты R14 √ R1 в сч╦тчике-защ╦лке R COUNTER LATCH устанавливают коэффициент деления опорного делителя. REFIN - это КМОП-вход с номинальным порогом VDD/2 и эквивалентным входным сопротивлением 100 кОм. Этот вход блокируется, когда инициирован режим пониженного энергопотребления Power-Down. Входы REFIN A и REFIN B являются входами (прямым и дополнительным, соответственно) входного радиочастотного каскада. Он представляет собой двухкаскадный усилитель-ограничитель, формирующий CML (Current Mode Logic) синхронизирующие уровни, необходимые для нормального функционирования прескалера. На вход REFIN A обычно пода╦тся сигнал от генератора управляемого напряжением (VCO). Дополнительный вход REFIN B, как правило, блокируется на землю через конденсатор ╦мкостью 100 пФ. CLK является входом синхронизации последовательности данных, поступающих со входа DATA. Загрузка последовательности данных DATA производится, начиная со старшего бита (MSB) и заканчивается двумя младшими контрольными битами. Каждый бит данных записывается в 24-разрядный входной регистр сдвига 24-BIT INPUT REGISTER по положительному фронту импульса CLK. CLK - это КМОП-вход с высоким полным входным сопротивлением. LE - это КМОП-вход разрешения загрузки. В течении всего времени загрузки данных в 24-разрядный входной регистр, уровень на этом входе должен быть низким. По окончании загрузки данных, после фиксации последнего (младшего) бита, когда уровень на этом входе принимает высокое состояние, данные из входного регистра загружаются в одну из четыр╦х защ╦лок LATCH. На рис. 2 показан упрощенный формат загрузки данных в 24-разрядный входной регистр сдвига. В табл. 2√5 привед╦н формат регистров-защ╦лок, используемых для программирования различных режимов ИМС ADF4110. Биты С2, С1 (DB1, DB0) используются для выбора защ╦лки. Таблица 2. Формат защ╦лки опорного делителя

*) X ≈ don`t care. Таблица 3. Формат защ╦лки N-делителя

Рисунок 2. Упрощенный формат загрузки последовательности данных

На рис. 2 обозначены:

CE - это вход выбора микросхемы. При высоком уровне на этом входе разрешается работа микросхемы. Логический низкий уровень на этом входе переводит устройство в режим Power-Down, а выход источника тока - в режим третьего состояния. RSET - вход установки максимального выходного тока источника. Резистор, включенный между этим входом и выводом CPGND (земля источника тока), устанавливает максимальный выходной ток источника тока. Номинальный потенциал напряжения на этом входе должен быть порядка 0,56 В. Взаимосвязь между выходным током и номиналом используемого резистора выражается отношением: Icp max = 23,5/RSET. (1) Так, при использовании резистора номиналом 2,7 кОм максимальный выходной ток источника тока будет равен 8,7 мА. CP - выход источника тока. Когда выход разреш╦н, сигнал управления через внешний фильтр нижних частот поступает на вход VCO. Как уже говорилось ранее, этот выход может принимать третье состояние в различных режимах функционирования ИМС. MUXOUT - выход мультиплексора, позволяет коммутировать на выход различные внутренние сигналы микросхемы. Состояние выхода контролируется битами M3, M2 и M1 в функциональной защ╦лке FUNCTION LATCH. Этот выход также может принимать третье состояние. Входы AVDD и AGND являются входами аналогового источника питания (аналоговой части микросхемы) и аналоговой земли, соответственно. Значение источника питания AVDD должно находиться в диапазоне от 2,7 до 5,5 В. Входы DVDD и DGND являются входами цифрового источника питания (цифровой части микросхемы) и цифровой земли, соответственно. Значение источника питания DVDD должно находиться в диапазоне от 2,7 до 5,5 В. По сути, значения источников питания AVDD и DVDD должны быть равны, и на практике, как правило, они соединены между собой, и питание на эти части микросхемы пода╦тся от общего для них источника питания VDD. Здесь необходимо сделать важное замечание относительно конденсаторов развязки, которые ставятся в цепях этих источников питания. Они (как впроч╦м и другие компоненты высокочастотных схем) должны быть расположены (припаяны) своими выводами к поверхности платы настолько близко, насколько это возможно, то есть, иными словами, должны иметь минимально возможную длину выводов. Эти сведения не претендуют на новизну, а являются скорее правилом хорошего тона при конструировании высокочастотной аппаратуры. Важно также отметить, что площадь заземляющей поверхности должна быть как можно больше и как можно лучшего качества. Аналоговая земля AGND и цифровая земля DGND на практике также соединяются между собой и представляют общую для этих источников питания землю GND. Vp и CPGND - вход питания и земля источника тока. Значение этого источника питания должно быть больше или равно VDD. В системах, где значение VDD равно 3 В, значение Vp может быть равно 6 В и использоваться для управления VCO с диапазоном настройки до 6 В. На этот вход пода╦тся напряжение от отдельного источника питания, хотя земля CPGND может быть соединена с общей земл╦й GND. Функционирование основных блоков ИМСДвухмодульный прескалер типа P (P + 1)Двухмодульный прескалер вместе со сч╦тчиками А и В образуют делитель с большим переменным коэффициентом деления N = BP + A. Значение сч╦тчика А лежит в диапазоне от 0 до 63, а значение В - от 3 до 8191. Прескалер, как уже говорилось выше, имеет фиксированные коэффициенты деления 8/9, 16/17, 32/33, 64/65 и представляет собой двухмодульный делитель с поддержкой разрешающей способности системы, о котором было рассказано во второй части цикла. Значения коэффициентов деления прескалера устанавливают биты P2 и P1 в FUNCTION LATCH. Такой прескалер, работающий с CML-уровнями, синхронизируется от входного радиочастотного сигнала и делит входную частоту до значения, при котором могут работать КМОП-сч╦тчики А и В. Сч╦тчики подключаются, когда прескалер имеет выходную частоту, равную 200 МГц (максимальная рабочая частота КМОП-сч╦тчиков при VDD = 5 В) или меньше. Так, для ИМС ADF4110 сч╦тчики будут определены, то есть подключены при любом значении коэффициентов деления прескалера, так как максимальная входная частота для этой микросхемы составляет 550 МГц, и при наименьшем коэффициенте деления прескалера мы получим выходную частоту, поступающую на сч╦тчики А и В, порядка 68 МГц (550/8 = 68,75), что удовлетворяет условию работы сч╦тчиков. Несколько иначе обстоит дело с другими ИМС этого семейства ADF4111, ADF4112 и ADF4113, которые отличаются от ADF4110 значением входной частоты, током потребления и шумовыми характеристиками. Так, для ADF4111 максимальная входная частота составляет 1,4 ГГц, для ADF4112 - 3 ГГц и для ADF4113 - 3,7 ГГц. При входной частоте, например в 2 ГГц (для ADF4112 или ADF4113), значение коэффициента деления прескалера, равное 8/9, не будет действовать, так как выходная частота прескалера будет равна 250 МГц, что противоречит условию подключения сч╦тчиков. В данном случае, сч╦тчики будут подключены только при коэффициенте деления 16/17 и выше. Режим ресинхронизации прескалераИнтересной особенностью работы прескалера является так называемый режим ресинхронизации, или восстановления синхронизации входной радиочастоты на выходе прескалера - RESYNCHRONIZING THE PRESCALER OUTPUT. Как говорилось выше, прескалер работает с входными CML-уровнями и синхронизируется от входного радиочастотного сигнала. Для того, чтобы восстановить эту синхронизацию на выходе прескалера, как раз и используется режим ресинхронизации. За этот режим отвечают два бита DLY и SYNC в R COUNTER LATCH. Когда бит DLY = 0, а SYNC = 1, на выходе прескалера происходит восстановление синхронизации входной радиочастоты. Это уменьшает флуктуационные помехи, вносимые прескалером, и улучшает суммарную характеристику фазового шума в синтезаторе. Когда DLY = 1 и SYNC = 1, ресинхронизация происходит с некоторой задержкой. Добавление задержки к RF-сигналу расширяет в некоторой степени рабочую частоту. Признак ресинхронизации (с задержкой или без не╦) устанавливается только когда SYNC = 1. С установленным признаком SYNC в работе синтезатора могут происходить сбои, обусловленные тем, что при некоторой выходной частоте в определ╦нный момент времени задержка через прескалер может совпасть с активным фронтом сигнала на радиочастотном входе, и это вызовет срыв SYNC-признака, а соответственно, и режим ресинхронизации. Поэтому этот режим следует использовать с некоторой осторожностью. Также при использовании SYNC-признака увеличивается ток потребления устройства. Нормальный режим работы прескалера устанавливается, когда SYNC = 0, а значение DLY - любое. А, В счетчикиЗначения сч╦тчиков А и В устанавливают биты A6√A1 и B13√B1, соответственно, в A, B COUNTER LATCH. Выражение, характеризующее формирование выходной частоты на выходе внешнего VCO имеет вид: fVCO = [(PxB) + A]xfREF IN/R, (2) где fVCO - выходная частота внешнего VCO; P - предварительный модуль прескалера; B - коэффициент деления 13-разрядного сч╦тчика В (от 3 до 8191); A - коэффициент деления 6-разрядного сч╦тчика A (от 0 до 63); fREF IN - входная опорная частота; R - коэффициент деления опорного делителя (14-разрядного сч╦тчика R с коэффициентом деления от 1 до 16383).

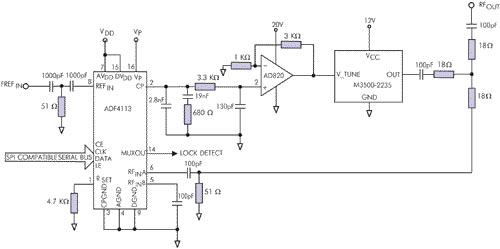

Фазовый детектор и источник токаФазовый детектор и источник тока такого же типа, как на рис. 4 предыдущей статьи ("Базовая схема, конструктивные блоки и шумовые характеристики ФАПЧ синтезаторов частоты"). Импульс antibacklash pulse width, формируемый элементом DELAY (рис. 4 вышеупомянутой статьи), гарантирует отсутствие "м╦ртвой" зоны в передаточной функции VCO и уменьшает фазовый шум и паразитные составляющие в спектре выходного сигнала. Рисунок 4. Схема широкодиапазонного ФАПЧ-синтезатора частоты

Шириной этого импульса можно управлять, используя два бита АВР2 и АВР1 в сч╦тчике-защ╦лке опорного делителя R COUNTER LATCH. Состоянием бита F2 в функциональной защ╦лке FUNCTION LATCH изменяют поляризацию фазового детектора. Когда F2 = 0 - негативная поляризация, когда F2 = 1 - позитивная. Источник тока также программируемый. Биты в FUNCTION LATCH CPI 3, CPI 2, CPI 1 устанавливают ток в режиме CURRENT SETTING 1, биты CPI 6, CPI 5, CPI 4 - ток в режиме CURRENT SET-TING 2. Установкой бита F3 в 1 в FUNCTION LATCH переводят выход источника тока в третье состояние. Выбором режима CURRENT SETTING 1 или CURRENT SETTING 2 управляет бит G1 (CP GAIN - усиление источника тока) в A, B COUNTER LATCH. Если G1 = 0, постоянно используется режим CURRENT SETTING 1, если G1 = 1 - режим CURRENT SETTING 2; при этом бит F4 (FASTLOCK ENABLE - разрешение режима Fastlock, быстрого блокирования) в FUNCTION LATCH должен быть сброшен, то есть равен 0, и запрещ╦н режим Fastlock. Режимы Fastlock 1 и Fastlock 2Биты F5 и F4 в FUNCTION LATCH отвечают за режим Fastlock. Если бит F4 = 1, разреш╦н режим Fastlock. Бит F5 устанавливает режим Fastlock 1 или Fastlock 2. При F5 = 0 устанавливается режим Fastlock 1, при F5 = 1 - режим Fastlock 2. Если установлен Fastlock 1, источник тока функционирует в режиме CURRENT SETTING 2. Устройство вводит режим Fastlock при G1 = 1 в A, B COUNTER LATCH. Устройство выходит из режима Fastlock при G1 = 0 и переключается в режим CURRENT SETTING 1. Когда установлен Fastlock 2, источник тока также функционирует в CURRENT SETTING 2, и устройство вводит режим Fastlock также при наличии 1, записанной в бит G1. Устройство выходит из этого режима под управлением таймера-сч╦тчика после периода ожидания, определяемого значением битов TC4 √ TC1 в FUNCTION LATCH; бит усиления G1 при этом автоматически сбрасывается, и устройство возвращается к нормальному режиму CURRENT SETTING 1. Чтобы прояснить ситуацию с программированием источника тока, необходимо заметить, что режим CURRENT SETTING 1 используется, когда выходная частота синтезатора стабильна и система в целом находится в статическом состоянии. Режим CURRENT SETTING 2 используется, когда система динамична и находится в состоянии изменения, то есть когда программируется новая выходная частота и происходит процесс синхронизации кольца ФАПЧ. Этот режим ещ╦ называют вспомогательным. Обычно поступают следующим образом: определяют необходимые значения токов для режимов CURRENT SETTING 1 и CURRENT SETTING 2 и устанавливают период времени (служебными битами TC4√TC1 в FUNCTION LATCH), в течении которого должен оставаться активным режим CURRENT SETTING 2. Как правило, значение тока в режиме CURRENT SETTING 2 больше, чем в режиме CURRENT SETTING 1. Это делается для того, чтобы быстрее произош╦л захват частоты. Как только пройд╦т период времени, определяемый битами TC4√TC1 (предполагается, что за этот период времени система станет статичной), установится нормальный режим CURRENT SETTING 1. Важной особенностью работы таймера-сч╦тчика является то, что этот режим разреш╦н только когда выбран режим Fastlock 2 установкой бита F5 в 1. Выходной мультиплексор и детектор блокировкиКак уже говорилось ранее, выходной мультиплексор MUX способен коммутировать на выход различные внутренние сигналы микросхемы. Это сигналы детектора блокировки LOCK DETECT, сигнал с выхода N делителя (прескалер с А и В сч╦тчиками), сигнал с выхода R делителя, сигнал SDOUT (выходная последовательность данных DATA) поступающий со специального выхода 24-разрядного регистра сдвига, и сигналы DVDD и DGND. При необходимости, выход мультиплексора может быть перевед╦н в третье состояние. Детектор блокировки состоит из детекторов двух типов: цифрового и аналогового. Соответственно, на выход MUXOUT может быть подан выходной сигнал одного из этих детекторов. Цифровой детектор имеет активный высокий уровень и может работать в двух режимах. Выбором режима управляет бит LDP в R COUNTER LATCH. Когда бит LDP = 0, должно пройти три последовательных цикла фазовой ошибки меньше 15 нс, прежде чем выход детектора блокировки примет активный уровень. Если бит LDP = 1, должно пройти пять последовательных циклов фазовой ошибки меньше 15 нс, прежде чем установится активный уровень на выходе детектора блокировки. Этот высокий уровень будет оставаться до тех пор, пока не будет обнаружена фазовая ошибка больше 25 нс на любом последующем цикле фазового детектора. То есть за активный уровень принимается высокий выходной сигнал, когда значение фазовой ошибки меньше заданного значения. Аналоговый детектор представляет собой N-канальный детектор с открытым стоком, который должен использоваться с внешним нагрузочным резистором номиналом 10 кОм. В данном случае активным выходным сигналом считается последовательность коротких импульсов высокого уровня. Режим Power-DownРежим пониженного энергопотребления Power-Down может быть установлен аппаратно или программно. Аппаратный асинхронный режим Power-Down устанавливается, когда уровень сигнала на входе СЕ принимает низкий уровень. Программный асинхронный режим Power-Down устанавливается, когда бит PD1 в FUNCTION LATCH равен 1, с условием, что бит PD2 = 0. Программный синхронный режим Power-Down устанавливается, когда биты PD1 и PD2 равны 1. В этом режиме устройство управляет источником тока, предотвращая нежелательные скачки частоты. Для установки программного режима Power-Down необходимо, чтобы уровень на входе CE был высоким. Здесь также необходимо отметить, что аппаратный режим Power-Down устанавливается независимо от состояния битов PD1, PD2 (естественно, когда на входе CE низкий уровень). При активизации режима Po-wer-Down (аппаратного или программного) происходит следующее:

Для восстановления нормального режима работы необходимо, чтобы на вход CE был подан сигнал высокого уровня, а бит PD1 должен быть установлен в 0 (бит PD2 может иметь любое значение). Защелка инициализацииПомимо рассмотренных ранее регистров-защ╦лок (R COUNTER LATCH, A, B COUNTER LATCH и FUNCTION LATCH), ИМС ADF4110 содержит ещ╦ защ╦лку инициализации INITIALIZATION LATCH, которая по внутреннему содержимому такая же, как функциональная защ╦лка FUNCTION LATCH. Она имеет такой же формат, как FUNCTION LATCH (табл. 4 и 5). Однако, когда запрограммирована защ╦лка INITIALIZATION LATCH, на сч╦тчики R и A, B дополнительно пода╦тся внутренний импульс сброса, который гарантирует, что в момент загрузки эти сч╦тчики фиксируют данные. Тем не менее, этот импульс не будет активизировать новый процесс загрузки данных. Если INITIALIZATION LATCH запрограммирована для синхронного режима Power-Down, внутренний импульс сброса перевед╦т устройство в Power-Down. Таблица 4. Формат функциональной защ╦лки

Таблица 5. Формат защ╦лки инициализации

На входной буфер опорного генератора, на входной радиочастотный каскад (входы REFIN A и REFIN B) и на прескалер этот импульс не воздействует. Следовательно, поддерживается процесс регулирования в кольце ФАПЧ. Существуют три варианта программирования микросхемы после включения питания. I. Программирование INITIALIZATION LATCH

При первоначальном программировании защ╦лки инициализации загружается содержимое функциональной защ╦лки, так как они имеют одинаковый формат. Внутренний импульс сбрасывает сч╦тчики R и A, B, которые находятся в режиме ожидания timeout до загрузки, а выход источника тока в режиме третьего состояния. Защ╦лкиваются первые данные в сч╦тчики А, В (значения коэффициентов деления) по внутреннему импульсу сброса, и начинается процесс регулирования в контуре ФАПЧ. Последующая загрузка данных А, В не будет осуществляться внутренним импульсом сброса, пока не будет новой инициализации. Чтобы запрограммировать новую выходную частоту, необходимо снова запрограммировать INITIALIZATION LATCH и загрузить новые коэффициенты деления сч╦тчиков А и В. В случае, когда INITIALIZATION LATCH запрограммирована для синхронного режима Power-Down, внутренний импульс сброса перевед╦т устройство в Power-Down. II. Асинхронный режим Power-Down по выводу CE и программирование FUNCTION LATCH

После этих действий начн╦тся процесс регулирования в контуре ФАПЧ. Необходимо учесть, что после установления уровня CE в высокое состояние может потребоваться промежуток времени в 1 мкс для того, чтобы система стала статичной (то есть произош╦л захват частоты в контуре ФАПЧ). Вывод СЕ может использоваться для контроля активности канала, пут╦м установления режима Power-Down. При этом не нужно каждый раз перепрограммировать устройство после выхода из Power-Down, достаточно того, что устройство было запрограммировано один раз после включения напряжения питания. Конечно, в случае, когда выходная частота должна изменяться, необходимо соответственно запрограммировать новые коэффициенты деления сч╦тчиков А, В в A, B COUNTER LATCH. III. Активизация счетчика сброса COUNTER RESET

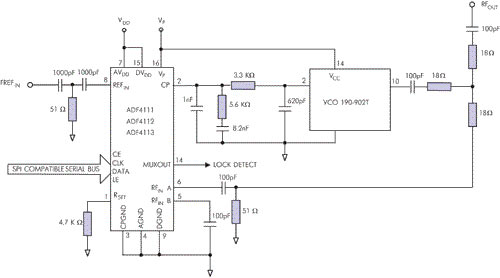

Бит F1 COUNTER RESET должен быть теперь равен 0 (запрет COUNTER RESET). Этот метод обеспечивает такой же режим программирования, как и метод инициализации. Он обеспечивает прямой контроль над внутренним импульсом сброса. Необходимо обратить внимание на то, что сч╦тчик сброса фиксирует данные А, В в момент загрузки и переводит источник тока в третье состояние, однако не переводит устройство в синхронный режим Power-Down. Этот метод сравним с методом инициализации, но требует дополнительной загрузки функциональной защ╦лки. Как уже говорилось ранее, ИМС ADF4110 представляет семейство простых однопетлевых ФАПЧ синтезаторов частоты. В эту подгруппу, помимо ADF4110, входят ИМС серий ADF4111, ADF4112 и ADF4113. Построение схемы синтезатора частоты с использованием ИМС этого семейства показано на рис. 3. Данная схема представляет собой узкополосный синтезатор частоты для беспроводных систем связи, таких как GSM, CDMA или WCDMA. В этой схеме применяется VCO компании Vari-L Corporation (http://www.vari-L.com). Выбор ИМС в конкретном случае обусловлен тем, что данная схема используется в качестве гетеродина передающей части базовой GSM станции со средней рабочей частотой 900 МГц (диапазон перестройки 880√915 МГц). Программирование производится при помощи последовательного интерфейса. Опорный сигнал имеет типичное значение для передающей части GSM-станции, равное 13 МГц. Разнесение между каналами - 200 кГц (стандарт GSM). ФНЧ спроектирован так, что полный фазовый сдвиг системы составляет 45º. Ширина полосы пропускания фильтра составляет 20 кГц, Чувствительность VCO - 12 МГц/В. Т-образная выходная конфигурация схемы с резисторами номиналом 18 Ом используется для согласования выхода VCO, входа RF ИМС и выхода RFOUT системы. Существует ряд приложений, где диапазон перестройки синтезатора должен составлять несколько сотен МГц. Так, в системах кабельного телевидения полный диапазон настройки должен составлять 400 МГц. На рис. 4 показана схема широкодиапазонного ФАПЧ синтезатора частоты, выполненного на ИМС ADF4113. В данном случае диапазон перестройки VCO расширен за сч╦т применения в цепи управления операционного усилителя AD820 и, соответственно, за сч╦т увеличения диапазона управляющего напряжения. Используемый VCO - Micronetics M3500-2235. Средняя выходная частота - 2900 МГц. Ширина полосы пропускания ФНЧ равна 40 кГц, частота, подаваемая на вход фазового детектора, равна 1 МГц. Чувствительность VCO - 90 МГц/В (на выходной частоте 2900 МГц). Полный фазовый сдвиг системы - 45º. С помощью ИМС семейства ADF4110/4111/4112/4113 можно строить схемы синтезаторов частот не только в классическом исполнении. ИМС этого семейства используются, например, в схемах прямых конверсионных преобразователей-модуляторов в передающих станциях. Более полную информацию относительно использования этих ИМС, а также подробный формат программирования этих ИМС можно получить на сайте компании ADI www.analog.com. Для первоначального освоения методов программирования этих микросхем и получения навыков работы с ними можно воспользоваться ADF4XXX evaluation Software, также находящемся на этом сайте. Там же приведена программа Loop Filter Design, позволяющая спроектировать необходимый фильтр нижних частот. В реальных применениях этих ИМС для управления режимами работы используются микроконтроллеры с соответствующим программным обеспечением и, в некоторых применениях, цифровые сигнальные процессоры, например, ADSP-21xx Digital Signal Processor. Микросхемы выполняются в корпусах TSSOP и CSP c числом выводов 16 и 20, соответственно. Литература

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

PDFs | Новости | Литература | Схемы | Форум | Блоги | Реклама |

ФАПЧ-синтезаторы частоты типа Integer-N.Часть 3.

ФАПЧ-синтезаторы частоты типа Integer-N.Часть 3.