|

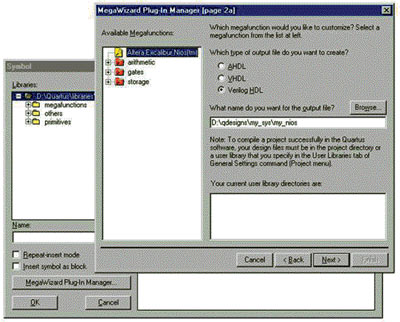

С. Хуторной Система Excalibur - средство разработки SoC-решений фирмы ALTERA. Часть 2. Процессор NiosМы продолжаем цикл статей посвященных пакету Excalibur фирмы Altera. В статье рассмотренны характеристики встраиваемого конфигурируемого процессора Nios.В следующих нормерах будут рассмотрены средства разработки аппаратного и программного обеспечения на базе системы Quartus и копмилятора Gnupro. Процесс проектирования в системе Excalibur начинается с выбора основного элемента проектируемой системы - процессора. Во избежание путаницы, следует предварительно определиться в понятиях. Excalibur - средство разработки систем на кристалле. Понятие "система" в этом случае объединяет все имеющиеся в наличии цифровые устройства и подсистемы, объедин╦нные в один кристалл ПЛИС. Процессор в такой системе является одной из подсистем, которая состоит из процессорного ядра (core) и окружающей его периферии (таймер, универсальный асинхронный при╦мопередатчик, различного рода порты ввода/вывода, встроенная память). В то же время, на плате, в которую встраивается ПЛИС, могут размещаться различные устройства, не попавшие, по той или иной причине, в кристалл, - это может быть дополнительная память, преобразователь уровней для последовательного порта и т.п. В дальнейшем описании они будут именоваться внешними устройствами - внешними по отношению к кристаллу ПЛИС. Для построения процессора используется САПР Quartus. Поэтому далее, параллельно с описанием процессора, по мере необходимости, будут рассматриваться некоторые особенности создания и верификации проекта в системе Quartus. Создание проекта начинается с ряда предварительных действий: определения директории проекта, имени проекта и логического объекта верхнего уровня при помощи мастера создания проектов New Project Wizard [1]. Любой проект, создаваемый в САПР Quartus, впрочем, как и в любом другом САПР, имеет иерархическую структуру. Как правило, логический элемент верхнего уровня, если он один, имеет название самого проекта. New Project Wizard состоит из тр╦х страниц - тр╦х этапов подготовки. На первом этапе (page, в терминологии Altera) выбирается папка проекта (по умолчанию, создаваемые проекты размещаются в папке qdesigns┘), его имя и имя логического объекта верхнего уровня. Далее производится подключение всех необходимых пользовательских библиотек. После того, как пройден предварительный этап, начинается процедура непосредственно проектирования. Непосредственно ввод проекта может производиться различными средствами: при помощи схемотехнического редактора (Block Diagram/Schematic), текстового редактора (на языках описания аппаратуры - AHDL, VHDL, Verilog HDL). Допустим, все предварительные мероприятия, связанные с созданием проекта, проведены: создана папка "my_sys", выбрано имя проекта и имя логического объекта верхнего уровня, создан Block Diagram/Schematic File с тем же именем. С этого момента начинается проектирование процессора. Как и в предыдущих версиях САПР фирмы Altera, таких как MAX+plus II, в пакете Quartus присутствует мощное средство, помогающее в создании или модификации того или иного цифрового блока на основе библиотеки мегафункций - MegaWizard Plug-in Manager. Процессор Nios - одна из встроенных мегафункций. На рис. 1 показано начало процесса создания любого элемента при помощи MegaWizard Plug-in Manager. Рисунок 1. Окно MegaWizard Plug-in Manager

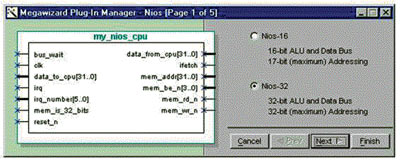

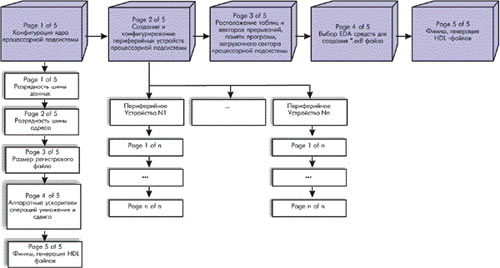

В окне Available Megafunctions (доступные мегафункции) выбираем пункт Altera Excalibur NiosTM. Создаваемый процессор назовем "my_nios". Собственно с этого момента начинается конфигурация процессора как подсистемы, состоящая из пяти этапов (рис. 2). Рисунок 2. Этапы (page) создания и конфигурации процессорной подсистемы проекта

Рисунок 3. Первый этап (page) создания и конфигурации ядра процессорной подсистемы проекта

На первой странице настройки Mega-Wizard Plug-in Manager предложит создать ядро процессора "my_nios_cpu". При этом конфигурация самого ядра процессора состоит из пяти этапов (рис. 2, 3). По ходу создания и настройки процессора необходимо ответить на ряд вопросов, связанных с его структурой [2]. Первый - разрядность процессора. Altera Excalibur Nios мегафункция позволяет создавать 16- и 32-разрядные процессоры. Соответственно, 16-разрядный процессор занимает меньше аппаратных ресурсов ПЛИС и является более быстрым. В табл. 1 приведены данные по ограничению адресуемой памяти и используемым аппаратным средствам для 16- и 32-разрядных процессоров. Таблица 1. Ограничение для 16- и 32-разрядных процессоров Nios

Предположим, что нам необходим 32-разрядный процессор (Page 1 of 5). Далее, на втором этапе конфигурации ядра (Page 2 of 5) предлагается выбрать разрядность шины адреса процессора. Этот параметр зависит от модели памяти процессора. Исполняемый код программы должен постоянно храниться в памяти, которая может находиться как вне кристалла ПЛИС, так и внутри его. В структуре кристалла ПЛИС имеются встроенные блоки ESB. Доступная ╦мкость этих блоков невелика, поэтому приложения, рассчитанные на встроенную в ПЛИС память, могут рассчитывать на ресурс, не превышающий 20 Кбайт (данные относятся к кристаллу EP20K200). Это требует ручной оптимизации исполняемого кода, что, как правило, достигается лишь с помощью ассемблера. Кроме того, если в процессе верификации возникнет необходимость в использовании встроенного анализатора SignalTapTM, то ресурс памяти может сократиться, потому что анализатору для хранения промежуточных данных необходимо наличие свободных ESB-блоков. Поэтому резонно для памяти программ и данных использовать внешнюю память. На отладочной плате, поставляемой вместе с пакетом Excalibur, размещена FLASH-память ╦мкостью 1 Мбайт и SRAM общей ╦мкостью 256 Кбайт [3]. Исходя из этого, разрядность шины адреса выбрана равной 21 бит. На следующей странице (Page 3 of 5) предлагается выбрать размер регистрового файла процессора. Максимально доступный размер - 512 регистров общего назначения - соответствует разрядности процессора. Доступ к регистрам производится с помощью скользящего регистрового окна, в котором одновременно может находиться 32 регистра %r0√%r31 [4]. Управление окном производится при помощи специальной инструкции ассемблера. Окно скользит дискретно, по 16 регистров. Регистровое окно делится на четыре части, согласно табл. 2. Таблица 2. Деление регистрового окна

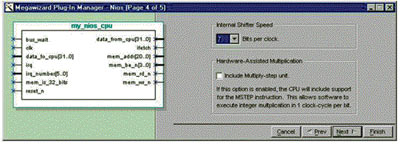

Нижние или младшие 8 регистров - глобальные регистры. При перемещении регистрового окна глобальные регистры остаются на месте, выходные регистры предыдущего окна становятся входными для следующего, а локальные и входные регистры предыдущего окна - недоступными. Помимо регистров общего назначения, процессор содержит специализированный 11-бит К-регистр, 33-бит регистр сч╦тчика команд PC (program counter) и 5 16-бит контрольных регистров %ctl0, %ctl1, %ctl2, %ctl8, %ctl9. Page 4 of 5 позволяет производить настройки внутреннего сдвигового регистра и аппаратного умножителя (рис. 4). Большинство алгоритмов цифровой обработки сигналов требует большого количества операций сдвига и умножения. Для реализации этих операций стандартными средствами процессора уходит много времени. Поэтому в современных DSP-процессорах используются аппаратные блоки операции MAC (Multiply And Accumulate). В процессорном ядре Nios существует возможность аппаратной поддержки операции умножения (MSTEP) и сдвига. В табл. 3 приведены данные по необходимому количеству дополнительных логических элементов при реализации аппаратного умножителя. Для операций сдвига также существует аппаратная поддержка, позволяющая производить за один цикл тактовой частоты процессора сдвиг до 31 бит.

Рисунок 4. Аппаратная поддержка операций умножения и сдвига

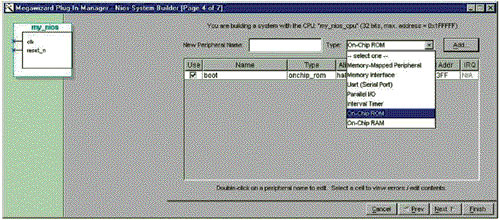

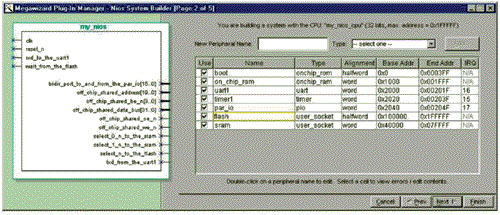

На последней странице конфигурации процессорного ядра (Page 5 of 5) система Quartus формирует файлы структуры ядра процессора с выдачей на экран отч╦та. На этом этап создания ядра процессора Nios закончен. Следующий шаг - создание подсистемы процессора со всеми необходимыми портами, таймерами, универсальными асинхронными при╦мопередатчиками, памятью и т.п. Всю системную периферию процессора можно условно разделить на 7 типовых групп (рис. 5, поле type): Рисунок 5. Конфигурация системной периферии процессора

Устройства, принадлежащие к какой-либо из групп, имеют свои настройки, общие для данной группы. Начн╦м с менеджера загрузки (boot на рис. 5). Он относится к классу On chip ROM - внутренняя память кристалла ПЛИС, в которую заносится программа загрузки процессорной системы. Сама программа генерируется при компиляции проекта, но исходный ассемблерный код е╦ доступен для редактирования, поэтому при необходимости процесс загрузки и инициализации может быть измен╦н. Задача boot-менеджера сходна с задачей системы BIOS персонального компьютера. При "включении питания" процессора (понятие "включить питание" для процессора, встраиваемого в ПЛИС, отличается от аналогичного для стандартного процессора, так как используемые в этом случае кристаллы энергозависимые) менеджер загрузки производит инициализацию всей подсистемы процессора и далее, по инструкции JMP, переда╦т управление исполняемому коду. Помимо этого, при отладке программного обеспечения с использованием отладочной платы, менеджер загрузки предоставляет дополнительные функции по мониторингу FLASH-памяти платы и ряд других необходимых функций. К числу настраиваемых параметров группы On Chip ROM относится ╦мкость памяти, выраженная в 16-бит словах (окно ROM Size) и путь к файлу содержимого ROM (ROM Input File) с расширением "mif". Параметры настройки On Chip RAM практически не отличаются от настроек ROM. Необходимо выбрать разрядность создаваемой области памяти (окно RAM Width) и е╦ размер (окно RAM Size), выраженный в количестве слов. Следующий элемент процессорной системы - таймер. Это единственный элемент, не требующий никакой аппаратной настройки, кроме выбора базового адреса и номера прерывания процессора. Программная настройка таймера значительно сложнее, однако не обязательна. В библиотеке функций для процессора Nios на языке С есть функция, позволяющая без дополнительных программных настроек использовать таймер как сч╦тчик интервалов времени. Для более тонкой программной настройки используются 6 регистров, доступных через базовый адрес, и соответствующее смещение (табл. 4). Таблица 4. Регистры для тонкой программной настройки

*) A2..А0 здесь и далее - смещение относительно базового адреса. Запись единицы в ячейку Start регистра управления запускает таймер; аналогично, при наличии единицы в ячейке Stop таймер останавливается. Регистр Snap позволяет делать мгновенные снимки содержимого сч╦тчика таймера. Для взаимодействия процессора с периферией как внутри кристалла, так и вне его, можно использовать два способа:

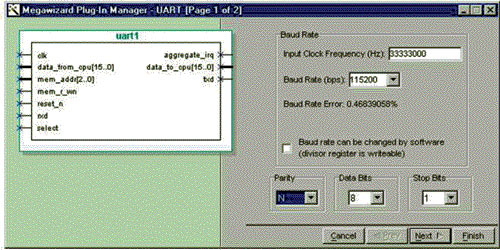

Рассмотрим первый способ. Он включает в себя два интерфейса: по-следовательный и параллельный. По-следовательный интерфейс рассмотрим на примере аппаратной и программной конфигурации UART. Аппаратная настройка периферийных устройств типа UART (универсальный асинхронный при╦мопередатчик) заключается в выборе ряда параметров: тактовой частоты (Input Clock Frequency, в нашем случае, 33333000 МГц) и скорости передачи (Baud Rate, 115200 бит/с). При аппаратной конфигурации можно ж╦стко установить скорость передачи, с запретом изменения е╦ программным способом (Baud rate can be changed by soft-ware, рис. 6). Существует возможность выбрать алгоритм проверки на ч╦тность (Parity), число передаваемых бит (Data bits) и число стоповых бит (Stop bits). Программный доступ к при╦мопередатчику осуществляется при помощи пяти 16-бит регистров (табл. 5). Используется упрощ╦нная логика интерфейса RS-232, в данной конфигурации UART не поддерживает сигналов аппаратного управления потоком данных CTS (Clear To Send) и RTS (Request To Send). Для полной совместимости с протоколом RS-232 необходим преобразователь уровней между ТТЛ-логикой выводов кристалла APEX и внешним кабелем. Таблица 5. Регистры, используемые для программного доступа к при╦мопередатчику

Рисунок 6. Окно настройки UART

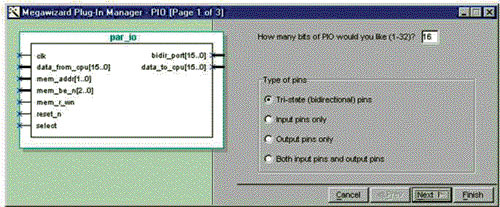

Для реализации параллельного интерфейса между процессором Nios и дополнительной аппаратурой как внутри кристалла ПЛИС, так и вне его, используется модуль типа Parallel I/O. Число этих модулей в составе процессора, или, иными словами, число параллельных портов, неограничено, и лимитируется лишь ╦мкостью самого кристалла. Аппаратная настройка этого элемента состоит из двух этапов (рис. 7, 8). На первом этапе (Page 1 of 3 на рис. 7) предлагается выбрать разрядность порта (How many bits of PIO would you like (1-32)?) и тип выводов (Type of pins): входные, выходные, двунаправленные и два первых типа одновременно. Рисунок 7. Первая страница настройки модуля Parallel I/O

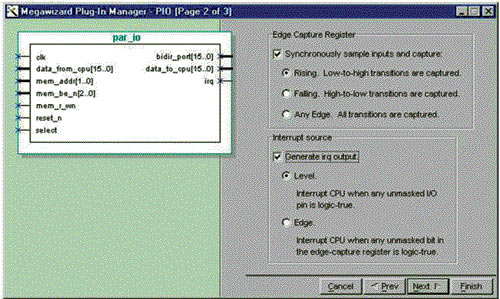

На второй странице настройки (Pa-ge 2 of 3, рис. 8) выбирается тип буферных регистров порта. Это могут быть либо синхронные регистры, управляемые по переднему или по заднему фронту, либо асинхронные. Выбор активируется установкой флага в окне Edge Capture Register. В окне Interrupt source имеется возможность выбора условия генерации прерывания процессора, либо по смене логического уровня в ячейке, либо по фронту. На этом аппаратная настройка порта закончена. Программное управление портом Parallel I/O осуществляется описанным выше UART и таймером аналогично, а именно, через регистры. Параллельный порт имеет три доступных для чтения и записи регистра (табл. 6). Рисунок 8. Вторая страница настройки модуля Parallel I/O

Таблица 6. Регистры для программного управления портом Parallel I/O

Как видно из таблицы, программная настройка порта позволяет настраивать его на битовом уровне, то есть каждый бит порта независимо от других может настраиваться:

Второй способ взаимодействия процессора с периферией - через память. К нему относятся два типа интерфейса: Memory Interface и Memory-Mapped Peripheral. Аппаратные настройки этих интерфейсов одинаковы ввиду их общности. Это интерфейсы памяти и периферии, отображаемой в памяти. Внешнее периферийное устройство, отображаемое в памяти, - это устройство, использующее совместную с процессором память. Доступ к такого рода периферии возможен через внешнюю память. Процесс аппаратной настройки такого рода периферии состоит из нескольких этапов. Для начала выбирается тип используемой памяти: On Chip или Off Chip. Далее необходимо выбрать разрядность шины данных и шины адреса. Чтение/запись в память может проводиться либо с использованием циклов ожидания, либо по сигналу готовности, аппаратная настройка позволяет выбрать один из этих режимов. На этом настройка периферии процессора закончена. На рис. 9 показан вид окна настройки периферии после выбора и конфигурации всех необходимых компонентов. Здесь имеется встроенная память ROM для хранения менеджера загрузки процессора (boot), встроенная память RAM (on_chip_ram), универсальный асинхронный при╦мопередатчик (uart1), таймер (timer1), 16-разрядный параллельный порт (par_io), интерфейсы с FLASH- и SRAM-памятью (flash и sram, соответственно). Каждому периферийному устройству присвоен свой базовый адрес и номер прерывания. Рисунок 9. Окно настройки периферии после выбора и конфигурации всех необходимых компонентов

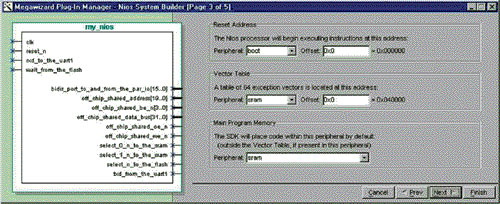

После того как было построено ядро процессора "my_nios_cpu", выбрана и настроена вся необходимая периферия процессорной системы, оста╦тся решить организационные вопросы (рис. 2, 10). Рисунок 10. Распределение памяти между системными устройствами

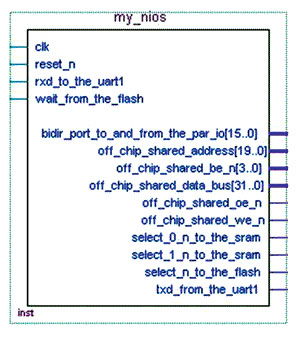

К таким вопросам относятся: с какого адреса при очередном сбросе процессора будет загружаться програм-ма boot-менеджера и какое системное устройство за это отвечает (Reset Address); где и по какому адресу будет находиться таблица векторов прерываний процессора (Vector Table); где будет находиться память программ (Main Program Memory)? САПР Quartus не имеет встроенных средств, позволяющих синтезировать процессорный модуль напрямую. Поэтому при построении процессора Quartus формирует файлы на языке VHDL или Verilog HDL, которые затем используются такими системами как Leonardo Spectrum для создания файла с расширением *.edf. И уже этот файл используется компилятором Quartus. В результате всех манипуляций, получили программно-аппаратный модуль, графический символ которого (рис. 11) можно использовать в Block Diagram/Schematic редакторе как отдельный элемент (мегафункцию) общей схемы. Рисунок 11. Изображение процессора Nios в Block Diagram/Schematic редакторе системы Quartus

Модульная структура проекта позволяет встраивать любое количество процессорных мегафункций в один проект и использовать его как основу для построения мультипроцессорных систем. При компиляции проекта, в котором используется процессор Nios, помимо общих папок и файлов, генерируемых системой Quartus при компиляции любого проекта, созда╦тся дополнитель-ная папка, необходимая для разработки программного обеспечения под созданный процессор - my_nios_custom_sdk. В не╦ входят папки inc и lib, где хранятся "заголовочные" файлы с расширением *.h и файлы библиотеки С, используемые компилятором и линковщиком GNUPro, а также папка пользовательских программ src. В данной статье основное внимание уделено построению процессора Nios и его аппаратной настройке. В то же время, встраиваемая система подразумевает наличие в кристалле ПЛИС дополнительной логики. Она может быть разработана как в САПР Quartus, так и в любом совместимом EDA (Electronic Design Automation) САПР. В следующей статье будет рассмотрен пример проектирования цифровой схемы в системе Quartus, имитационное моделирование (Simulation Mode), контроль сигналов внутри ПЛИС при помощи логического анализатора SignalTap. Литература:

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

PDFs | Новости | Литература | Схемы | Форум | Блоги | Реклама |

Система Excalibur - средство разработки SoC-решений фирмы ALTERA. Часть 2. Процессор Nios

Система Excalibur - средство разработки SoC-решений фирмы ALTERA. Часть 2. Процессор Nios